# 遷移故障向け診断テスト生成の一手法

小野 廉二<sup>1,a)</sup> 大竹 哲史<sup>1,2,b)</sup>

概要:本稿では、遅延故障を対象とした故障診断テスト生成法を提案する.故障診断テストは、与えられた故障ペアを区別するパターンである.縮退故障向けの故障診断テスト生成法としては、回路疑似変換により通常の縮退故障用テスト生成ツールを用いて故障診断テストを生成する手法が提案されている.遅延故障向けの診断テスト生成法としては、遷移故障テスト生成問題を2時刻展開モデル上の縮退故障のテスト生成問題に帰着し、縮退故障向けの手法と同様の概念を用いた回路疑似変換による方法が提案されている.本研究では、遷移故障モデル用テスト生成ツールを用いた、新しい回路疑似変換による遷移故障診断テスト生成法を提案する.従来法が遷移故障を区別する条件を2時刻展開により組合せ回路として表現するのに対し、提案法では2時刻の順序的な条件として表現する.従来法では1故障ペアに対して複数回のテスト生成が必要で、2時刻展開モデルを用いることにより対象回路の最大4倍のサイズの回路を扱わなければならない。これに対し、提案法では1故障ペアに対して1回のテスト生成のみで、扱う回路サイズも対象回路の2倍のサイズとなり、テスト生成の負荷が軽減できると期待できる。また、スキャン設計された順序回路をそのまま扱うことで、スキャンテストパターンを直接生成できるという特長を持つ。本稿では、提案法に市販のテスト生成ツールを用いることができることを、ISCAS'89ベンチマーク回路 s27を用いたケーススタディにより示す。

キーワード:遅延故障診断,故障診断テスト生成,遷移故障テスト生成ツール

# A Method of Diagnostic Test Generation for Transition Faults

RENJI ONO<sup>1,a)</sup> SATOSHI OHTAKE<sup>1,2,b)</sup>

Abstract: In this paper, we propose a method of diagnostic test generation for transition faults. A diagnostic test distinguishes a given pair of faults. For stuck-at faults, several methods of diagnostic test generation using an ordinary stuck-at ATPG tools based on circuit pseudo-transformation have been proposed. For transition faults, a method of diagnostic test generation has also been proposed. The method utilizes two-timeframe model with a stuck-at ATPG tool. The method needs to handle a quadruple circuit of a given circuit and multiple test generation for a pair of faults. In this work, we propose a new diagnostic test generation method for transition faults using an ordinary transition fault ATPG tool based on circuit pseudo-transformation. By using this method, we expect that the diagnostic test generation effort for transition faults can be reduced compared with the previous method. In this paper, we also show that a commercial transition fault ATPG can be utilized in our proposed method through a case study using circuit s27 of the ISCAS'89 benchmark set.

${\it Keywords:}\ {\it delay}\ {\it fault}\ {\it diagnosis},\ {\it diagnostic}\ {\it test}\ {\it generation},\ {\it transition}\ {\it fault}\ {\it ATPG}$

#### 1. はじめに

近年,半導体技術の進歩により,大規模集積回路 (VLSI) の高集積化・高速化が進んでいる。それに伴い,回路中の故障の種類も多岐にわたり増大をしており,さまざまな故

大分大学工学部 Oita Uniersity 大分市旦野原 700 番地

<sup>&</sup>lt;sup>2</sup> 科学技術振興機構 戦略的創造研究推進事業 JST-CREST

a) v1053015@oita-u.ac.jp

b) ohtake@oita-u.ac.jp

IPSJ SIG Technical Report

障が発生している。それらの中には従来の縮退故障モデルだけでは検出及び診断が困難な故障が増加している。例えば、高速に動作する回路においては、その動作タイミングに影響を与える遅延故障などがある。この故障に対するテスト及び故障診断が重要となってきている。特に、故障箇所、故障原因を特定することのできる故障診断テストの高い品質が求められている。本稿では、与えられた故障ペアを区別する(それぞれの故障により故障した回路の出力が異なる)パターンを生成する故障診断テスト生成を扱う。

縮退故障向けの故障診断テスト生成法としては, 回路 疑似変換により通常の縮退故障用テスト生成ツールを用 いて故障診断テストを生成する手法 [1][2] が提案されてい る. 遅延故障向けの診断テスト生成法としては、縮退故障 ATPG を用いた故障診断生成法が提案されている [3][4]. この手法では、遷移故障を対象として縮退故障 ATPG を 用いてテスト生成を行うので、2時刻展開モデルを用いる. [1][2] と同様の概念を用いた回路疑似変換により遷移故障 診断テスト生成をする. この手法では、1 故障ペアに対し て複数回のテスト生成が必要になる場合があり、回路疑似 変換により対象回路の最大4倍のサイズの回路を扱わなけ ればならない. 提案法では, 遷移故障 ATPG を用いた回路 疑似変換による遷移故障診断テスト生成法を提案する. 従 来法と違い2時刻展開モデルを用いないので、回路疑似変 換を行った際に扱う回路サイズは2倍となり、また、1故 障ペアに対して1回のテスト生成で診断テストを生成でき る. 提案法の有効性を ISCAS'89 ベンチマーク回路 s27 を 用いたケーススタディにより確認する.

本稿では、2節で故障ペアの区別可能性条件、故障非検出条件を定義する。3節では提案法として、遷移故障向けの診断テスト生成の一手法を提案し、例を用いて提案法の説明をする。4節ではISCAS'89ベンチマーク回路を用いた実験結果を示す。

#### 2. 諸定義

## 2.1 対象回路モデル

本研究において、故障診断テスト生成対象回路は完全スキャン設計 [5] されているものとする。また、2 パターンテストの印加には、ランチ・オフ・キャプチャ(LoC)方式を用いるものとする [6].

#### 2.2 区別可能性

故障ペア区別可能性条件,故障非検出条件として文献 [3] で定義されている条件を使用する. それらの条件を以下に示す.

定義 1 故障  $f_1, f_2$  からなる故障ペア  $f_p$  に対して、テストパターン  $t_1, t_2$  を印加したとき、次の条件のうち少なくとも 1 つが成立すれば、故障ペア  $f_p$  は区別できるという。 D1: 故障  $f_1$  が検出され、故障  $f_2$  が検出されない.

D2: 故障  $f_2$  が検出され、故障  $f_1$  が検出されない.

D3: 故障  $f_1,f_2$  が異なる外部出力で検出される.  $\Box$  故障の区別条件 D1,D2 を満たすためには,故障ペアの一方の故障を非検出とする必要がある.

定義 2 テストパターン  $t_1,t_2$  を印加したとき,信号線 l の  $w \to \overline{w}(w \in \{0,1\})$  の遷移故障は次の条件を少なくとも 1 つを満たすとき非検出という.

$U1:t_1$  で信号線 lに  $\overline{w}$  を設定

$U2:t_2$  で信号線 lに w を設定

$U3:t_2$  で信号線 lの w 縮退故障を非検出

## 3. 提案法

本稿では、遷移故障 ATPG を用いた回路疑似変換による遷移故障診断テスト生成法を提案する。本手法では、1 故障ペアに対して1回のテスト生成のみで故障ペアが区別可能か判断することができ、区別可能な場合には故障診断テストを生成する。本手法では、故障診断テスト生成の際にテスト生成の対象回路を変更する回路疑似変換を行う。回路疑似変換によって作られる回路は故障診断テスト生成時のみ用いるものであり、実際に回路を変換するテスト容易化設計とは異なる。3.1 節で提案法における回路疑似変換の説明をする。

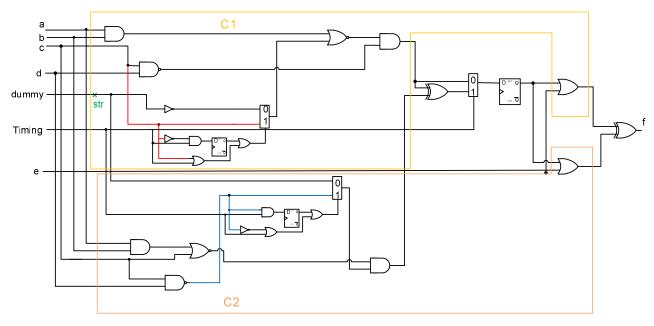

#### 3.1 回路疑似変換

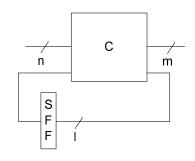

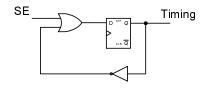

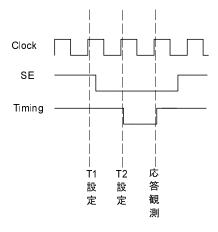

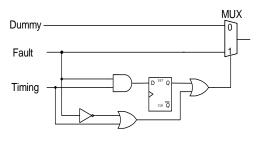

本手法の回路疑似変換を図1,2を用い説明する. 図1に, 与えられた完全スキャン順序回路を示す.入力(PI)は nビット, 出力 (PO) はmビットとし,lビットのスキャン フリップフロップ(SFF)及び組合せ回路 C で構成される ものとする.ここで、C の故障ペア  $fp(f_1,f_2)$  の故障を区 別することを考える. 故障  $f_1$  を立上り遷移故障, 故障  $f_2$ を立下り遷移故障とする. 本手法による回路疑似変換を図 2に示す. 故障  $f_1$  を仮定する故障信号線を切断し, 本手 法で提案する付加回路に接続する. そして, 付加回路の出 力を切断した箇所に繋ぎ直す. 故障 f2 を仮定する故障信 号線を切断し、本手法で提案する付加回路に接続する. そ して,付加回路の出力を切断した箇所に繋ぎ直す.故障ペ アの各故障に対して付加する回路は2種類あり、信号線の 故障が、立上り遷移故障と立下り遷移故障で付加する回路 が異なる. これについてはそれぞれ 3.2 節, 3.3 節で説明 する. 信号線 Timing は, LoC 方式の 2 パターンテストで のタイミングを制御する回路 [7] からの出力である. 回路 図及びタイミングチャートをそれぞれ図3,4に示す.信 号線 Dummy に故障を想定することによって,二重故障テ スト生成問題を単一故障テスト生成問題に帰着する. 信号 線 Dummy に想定する故障は立上り遷移故障である. C1 からの出力と C2 からの出力について、各ビットの排他的 論理和をとる. 信号線 Dummy の故障を検出可能なテスト パターンを生成できればいずれかの排他的論理和の出力が

図1 完全スキャン順序回路

Fig. 1 A full-scan sequential circuit

図 2 回路疑似変換

Fig. 2 Circuit-pseudo transformation

1となり、C1と C 2の出力が異なる。このことから故障  $f_1, f_2$  を区別可能であることがわかる。各ビットのフリップ フロップの入力はマルチプレクサにより選択を行い、LoC テストを実現する。テストパターン印加後、応答観測の際 に制御信号が 0となる。本手法では、このような回路疑似 変換を行い故障診断テスト生成を行う。

#### 3.2 立上り遷移故障活性化制御回路 (STRACC)

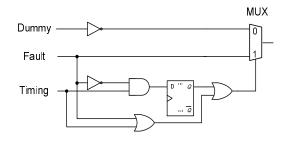

立上り遷移故障活性化制御回路の回路を図5に示す.区別対象故障が立上り遷移故障の場合,この回路を付加する.信号線 Fault には,故障信号線を繋ぎ,信号線 Timing は図3の出力を繋ぐ.信号線 Dummyに立上り遷移故障を想定し,信号線 Dummyの故障を検出することを目指す.信号線 Dummyの故障を検出することを目指す.信号線 Dummyの故障を検出するためには,故障の影響を回路の外部出力に伝搬させなければいけない.故障の影響を外部出力へ伝搬させるには,2パターンテストでの2パターン目でマルチプレクサの制御信号を0としなければならない.マルチプレクサの制御信号を0とするには2パターンテストの1パターン目で信号線 Faultに0,2パターン目で信号線 Faultに1を設定すればよい.すると,回路疑似変換前の回路の故障信号線において故障を活性化することができる.表1に回路の動作表を示す.

図3 タイミング制御回路

Fig. 3 Timing control circuit

図 4 タイミングチャート

Fig. 4 Timing chart

#### 3.3 立下り遷移故障活性化制御回路(STFACC)

立下り遷移故障活性化制御回路の回路を図6に示す。区別対象故障が立下り遷移故障の場合,この回路を付加する。信号線 Fault には故障信号線を繋ぎ,信号線 Timing は図3の出力を繋ぐ。立上り遷移故障活性化回路と同様に,信号線 Dummy の故障を検出することを目指す。信号線 Dummy の故障を検出することを目指す。信号線 Dummy の故障を検出することを目指す。信号線 Dummy の故障を検出するためには,故障の影響を回路の外部出力へ伝搬させなければいけない。故障の影響を外部出力へ伝搬させるには,2パターンテストの2パターン目でマルチプレクサの制御信号を0としなければならない。マルチプレクサの制御信号を0とするには2パターンテストの1パターン目で信号線 Fault に1、2パターン目で信号線 Fault に0を設定すればよい。すると,回路疑似変換前の回路の故障信号線において故障を活性化することができる。表2に回路の動作表を示す。

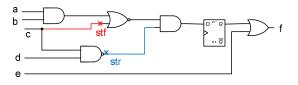

#### 3.4 適応例

図 7 を用いて具体的に故障診断テスト生成を説明する. この回路は 5 入力,1 出力,1 スキャン FF をもつ順序回路である。故障ペア  $fp(f_1,f_2)$  の区別を考える。故障  $f_1$  は立下り遷移故障であり,故障  $f_2$  は立上り遷移故障である。この故障ペアを区別するために,本手法を用いて回路疑似変換を行うと図 10 のようになる。生成されたテストパターンの 1 パターン目を  $t_1$  、2 パターン目を  $t_2$  、スキャン入力を  $test\_si$  とする。生成されたテストパターンは  $test\_si=0$

000\_00

図 5 立上り遷移故障活性化制御回路 (STRACC)

Fig. 5 Slow to rise activation control circuit(STRACC)

表 1 STRACC 動作表 **Table 1** A table of STRACC

| 1 パターン目 |    |             | 2 パターン目 |    |             |

|---------|----|-------------|---------|----|-------------|

| Fault   | FF | 制御信号値 (MUX) | Fault   | FF | 制御信号値 (MUX) |

|         |    |             | 0       | 0  | 1           |

| 0       | *  | *           | 1       | 0  | 0           |

|         |    |             | 0       | 1  | 1           |

| 1       | *  | *           | 1       | 1  | 1           |

図 6 立下り遷移故障活性化制御回路 (STFACC)

Fig. 6 Slow to fall activation control circuit(STFACC)

表 2 STFACC 動作表

Table 2 A table of STFACC

| 1 パターン目 |    |             | 2 パターン目 |    |             |

|---------|----|-------------|---------|----|-------------|

| Fault   | FF | 制御信号値 (MUX) | Fault   | FF | 制御信号値 (MUX) |

|         |    |             | 0       | 1  | 1           |

| 0       | *  | *           | 1       | 1  | 1           |

|         |    |             | 0       | 0  | 0           |

| 1       | *  | *           | 1       | 0  | 1           |

$$t_1 = (a, b, c, d, e) = (0, 1, 1, 0, 1)$$

$t_2 = (a, b, c, d, e) = (0, 0, 0, 0, 1)$

となる. このテストパターンを回路疑似変換前の回路に印加すると、故障ペア  $fp(f_1,f_2)$  のうち、故障  $f_1$  のみを検出することができるので、故障ペアを区別することができている. 提案法では、このようにして故障ペアを区別する診断テストを生成する.

# 4. 実験

本研究では、提案手法が市販のテスト生成ツールを用いて故障診断テスト生成が行えることを確認した。実験には、ISCAS'89 ベンチマーク回路 s27 を用いた.

図7 回路例

Fig. 7 An example of a circuit

Fig. 8 The flow of experiments

S I

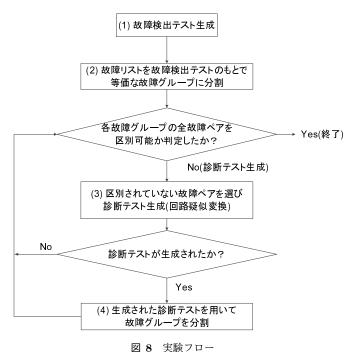

#### 4.1 実験フロー

図8に実験フローを示す.表3に実験環境を示す.テスト生成ツールにはTetraMAX(Synopsys社)を用いた.また,ベンチマーク回路のスキャン設計にはDesign Vision(Synopsys社)を用いた.

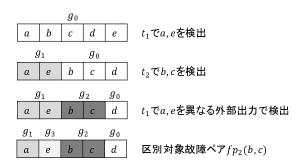

実験フローの(1)では、TetraMAX を用いて故障検出テスト生成を行う。(2)では、(1)の情報をもとに故障グループ分割をする。故障グループ分割の方法を図 9 を用いて説明する。全ての故障は最初はグループ  $g_0$  に属する。故障検出テストにおいて、テストパターン  $t_1$ 、 $t_2$  で故障 a,b,c,d,e が検出されたとする。テストパターン  $t_1$  で故障 a,e のみが検出されると、故障 a,e がグループ  $g_0$  から分割され、グループ  $g_1$  とする。 $t_2$  では、故障 b,c のみが検出されると、故障 b,c がグループ  $g_2$  とする。ここで、故障ペア  $f_1(a,e)$ ,  $f_2(b,c)$  が得られる。次に、こ

表 3 使用した計算機

Table 3 A teble of used computer

| CPU       | Intel Xeon X5675 3.06GHz  |

|-----------|---------------------------|

| メモリ       | 40GB                      |

| テスト生成ツール  | TetraMAX(Synopsys 社)      |

| スキャン設計ツール | Design Vision(Synopsys 社) |

図 10 回路疑似変換例

Fig. 10 An example of circuit-pseudo transformation

図 9 グループ分割

Fig. 9 Divided into groups

の故障ペアに対して,2節で定義した故障ペア区別可能性 条件 D3 を満たすものを,テストパターン  $t_1,t_2$  で探す. $t_1$ では,a,e を異なる外部出力で検出することができるので, 故障 e がグループ  $g_1$  から分割され,グループ  $g_3$  とする. すると,故障ペア  $fp_2(b,c)$  が得られる.提案法では,この 故障ペア  $fp_2(b,c)$  を区別することを考える.

(3) 以降の処理が提案法となる. (3) では区別されていない故障ペアを選び,回路疑似変換を行い故障診断テスト生成をする. (4) では故障診断テストが生成された場合,生成されたテストパターンを用いて故障グループの分割を行う.

# 4.2 実験結果

ISCAS'89 ベンチマーク回路 s27 の故障検出テストの結果及び、提案法を用いた故障診断テストの結果をそれぞれ表 4, 5 に示す.総故障数は 49 であり、故障検出テストをもとにグループ分割を行うと総グループ数は 34, そのうち故障が 2 つ以上のグループは 11 である.区別できていな

表 4 故障検出テスト Table 4 Detect test

| 故障検出テスト数        | 15   |

|-----------------|------|

| テスト生成時間(秒)      | 0.02 |

| 総故障数 (代表故障のみ)   | 49   |

| 総グループ数          | 34   |

| 故障が 2 つ以上のグループ数 | 11   |

| 総故障ペア数          | 20   |

表 5 故障診断テスト Table 5 Diagnostic test

| 故障診断テスト数   | 15   |

|------------|------|

| テスト生成時間(秒) | 0.45 |

| 区別可能故障ペア数  | 17   |

| 区別不可能故障ペア数 | 3    |

い総故障ペア数は 20 あり、本実験ではこれらすべての故障ペアに対して診断テスト生成を試みた。本手法の結果として、区別可能となった故障ペアの数は 17、区別ができないと判明した故障ペアの数は 3 となった。

#### まとめ

本論文では、遷移故障向け診断テスト生成法を提案した. 実験として、与えられた故障ペアに対して、回路疑似変換を行うことによって区別可能か判定をした.今後の課題としては、回路疑似変換の自動化を図り大規模回路への対応することなどが挙げられる.

謝辞 本研究は東京大学大規模集積システム設計教育研究センターを通しシノプシス株式会社の協力で行われた ものである.本研究は一部,科学研究費補助金(課題番号

#### 情報処理学会研究報告

IPSJ SIG Technical Report

22700054) の助成を受けたものである.

#### 参考文献

- V. D. Agrawal, D. H. Baik, Y. C. Kim and K. K. Saluja: Exclusive test and its applications to fault diagnosis, in *Proc. of VLSI Design*, Paper 1145, 2003.

- [2] Y. Zhang and V. D. Agrawal: A diagnostic test generation system, in *Proc. of International Test Conference*, Paper 12.3, 2010.

- [3] Y. Higami, Y. Kurose, S. Ohno, H. Yamaoka, H. Takahashi, Y. Shimizu, T. Aikyo and Y. Takamatsu: Diagnostic test generation for transition faults using a stuck-at ATPG tool, in *Proc. of International Test Conference*, Paper 16.3, 2009.

- [4] Y. Higami, S. Ohno, H. Yamaoka, H. Takahashi, Y. Shimizu and T. Aikyo: Generation of diagnostic tests for transition faults using a stick-at ATPG tool, *IEICE Transaction on Information and Systems*, Vol.95, No.4, pp.1093-1100, Apr.2012.

- [5] M. Abramovici, M. A. Breuer, and A. D. Friedman: Digital system testing testable design, IEEE Press,1990.

- [6] A. Krstic, and K. T. Cheng: Delay Fault Testing for VLSI Circuits, IEEE Press, 1998.

- [7] 本田太郎, 大竹哲史: 遅延故障 BIST 向け LFSR シード生成法, 信学技報 (DC2013-58), No.321, pp.227-231,2013.